It is easier and cheaper to get a PLD than any of the other ASIC's. Companies can buy software and hardware to make their own PLD. But to get any of the other three, you must ask another company to make it for you.

Contents • • • • • • • • • • • • Early programmable logic [ ] In 1969, offered the XC157, a mask-programmed gate array with 12 gates and 30 uncommitted input/output pins. In 1970, developed a mask-programmable IC based on the read-only associative memory or ROAM. This device, the TMS2000, was programmed by altering the metal layer during the production of the IC. The TMS2000 had up to 17 inputs and 18 outputs with 8 for memory. TI coined the term (PLA) for this device. In 1971, Company (GE) was developing a programmable logic device based on the new (PROM) technology.

This experimental device improved on IBM's ROAM by allowing multilevel logic. Intel had just introduced the floating-gate erasable PROM so the researcher at GE incorporated that technology. The GE device was the first erasable PLD ever developed, predating the EPLD by over a decade. GE obtained several early patents on programmable logic devices.

In 1973 introduced a mask-programmable PLA device (DM7575) with 14 inputs and 8 outputs with no memory registers. This was more popular than the TI part but cost of making the metal mask limited its use. The device is significant because it was the basis for the field programmable logic array produced by in 1975, the 82S100. ( actually beat Signetics to market but poor yield doomed their part.) In 1974 GE entered into an agreement with (MMI) to develop a mask–programmable logic device incorporating the GE innovations. The device was named the 'Programmable Associative Logic Array' or PALA. The MMI 5760 was completed in 1976 and could implement multilevel or sequential circuits of over 100 gates.

The device was supported by a GE design environment where Boolean equations would be converted to mask patterns for configuring the device. The part was never brought to market.

Offline installer mcafee. And internet. It saves internet bandwith & time when downloading windows installation files.

Main article: In 1970, developed a mask-programmable IC based on the read-only associative memory or ROAM. This device, the TMS2000, was programmed by altering the metal layer during the production of the IC. The TMS2000 had up to 17 inputs and 18 outputs with 8 JK flip flop for memory.

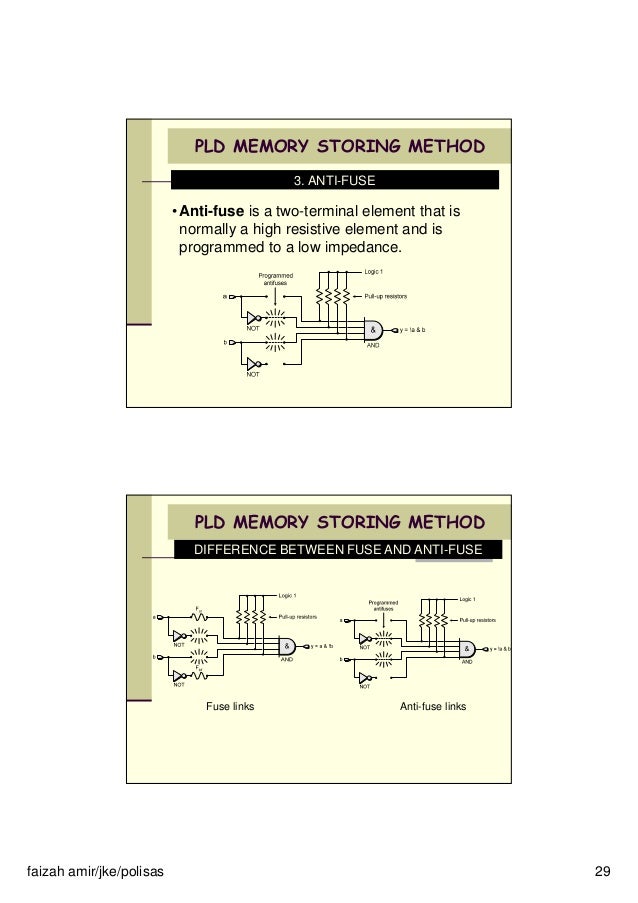

TI coined the term for this device. A programmable logic array (PLA) has a programmable AND gate array, which links to a programmable OR gate array, which can then be conditionally complemented to produce an output. Main article: PAL devices have arrays of transistor cells arranged in a 'fixed-OR, programmable-AND' plane used to implement 'sum-of-products' binary logic equations for each of the outputs in terms of the inputs and either synchronous or asynchronous feedback from the outputs. MMI introduced a breakthrough device in 1978, the or PAL. The architecture was simpler than that of Signetics FPLA because it omitted the programmable OR array. This made the parts faster, smaller and cheaper. They were available in 20 pin 300 mil DIP packages while the FPLAs came in 28 pin 600 mil packages.

The PAL Handbook demystified the design process. The PALASM design software (PAL assembler) converted the engineers' Boolean equations into the fuse pattern required to program the part. The PAL devices were soon by National Semiconductor, Texas Instruments and AMD. After MMI succeeded with the 20-pin PAL parts, introduced the 24-pin PAL with additional features. After buying out MMI (1987), AMD spun off a consolidated operation as, and that business was acquired by in 1999. Lattice GAL 16V8 and 20V8 An improvement on the PAL was the generic array logic device, or GAL, invented by in 1985. This device has the same logical properties as the PAL but can be erased and reprogrammed.

The GAL is very useful in the prototyping stage of a design, when any in the logic can be corrected by reprogramming. GALs are programmed and reprogrammed using a PAL programmer, or by using the technique on supporting chips. Lattice GALs combine and electrically erasable (E 2) floating gate technology for a high-speed, low-power logic device. A similar device called a PEEL (programmable electrically erasable logic) was introduced by the International CMOS Technology (ICT) corporation. Main article: PALs and GALs are available only in small sizes, equivalent to a few hundred logic gates.

For bigger logic circuits, complex PLDs or can be used. These contain the equivalent of several PALs linked by programmable interconnections, all in one. CPLDs can replace thousands, or even hundreds of thousands, of logic gates. Some CPLDs are programmed using a PAL programmer, but this method becomes inconvenient for devices with hundreds of pins. A second method of programming is to solder the device to its printed circuit board, then feed it with a serial data stream from a personal computer.